# Structural Analysis of Efficient Error Control Scheme in PLC Environment

Zaveri Himani

Computer Science & Engineering

Parul Institute of Engineering and Technology

Limda, Gujarat

Vala Brijesh

Computer Science & Engineering

Parul Institute of Engineering and Technology

Limda, Gujarat

#### **ABSTRACT**

Turbo codes are attractive compared with Low Density Parity Check (LDPC) codes for Forward Error Correction (FEC) applications mainly due to their better performance, specially at low Signal-to-Noise Ratio (SNR) as are common in Powerline channels. Turbo Code is patented hence it is costlier for HomePlug device so it cannot be used. For small block length other code like LDPC which gives better performance as Turbo Code but at low SNR. Complexity of LDPC is increased when block length increase and it works well with low code rate. Complexity of Polar code is not increase even though its block length increases. The objective of this paper is to implement Polar code on PLC Channel to reduce the complexity and improve BER using specific Block Length.

#### **General Terms**

Channel Capacity, Performance, Polar Codes, QC-LDPC

#### Keywords

PLC, Code rate, Complexity

### 1. INTRODUCTION

PLC has been recent trend as a subject of research work [1-4]. The main inspiration behind this research work is to, now-adays we are using internet service like IPod, TV, Mobile, Computer etc. everywhere in our house. For using all these equipment parallel high data rate is required, but our wireless router are not capable and laying new cable like Ethernet throughout the house become complicated. Thus, PLC provides a convenient and cost-effective solution for data transmission. PLC Channel use power line i.e. existing wiring in our house to transmit data over Powerline. Challenges in power line are Signal attenuation and noise present in power line. That noise can be overcome by using channel coding Scheme.Like other technologies, PLC also faces its challenges. The Powerline network has not been designed for communication purposes and not favourable for transmission medium. Unlike other channels power line doesn't represent an additive white Gaussian noise (AWGN) environment. Noise in power-lines has the cyclic nature for power voltage [5, 6]. Such cyclic nature of power line noise is called "cyclostationary" [6]. PLC systems have to apply efficient and robust modulation and coding schemes. To achieve reliable communications using power lines, it is necessary to use channel coding technique. LDPC Codes [5-7] are capable to achieve capacity of channel which is nearer to those defined by Shannon on an AWGN channel by using iterative decoding. So, LDPC Codes have enough capability to be candidates. The authors of [8] have shown the comparison that LDPC codes can perform better than convolutional codes or Reed-Solomon on PLC channel. In [10], it was found that

the performance of LDPC codes is superior to that of the Turbo codes [9] under a cyclostationary Gaussian noise environment. Disadvantage of using the Turbo codes is the requirement to pay patent fees for every turbo code enabled device because it is licensed. So, it is necessary to examine possible LDPC coding strategies that may provide viable alternatives for FEC coding in future PLC systems. While the increase in block lengths is known to result in improved performance of LDPC codes, this increase is accompanied by increase in implementation complexity. So, as per paper [11] QC-LDPC codes which is less complex and require much less memory and are easier to implement. The paper [11] shows that QC-LDPC can approximate the error rates of Turbo codes even at low SNRs and can significantly reduce the BER at higher SNRs for systems by appropriately selecting code rate and block length real power line noise. But in QC-LDPC, complexity and performance is issue. So, motto of this paper to solve issue related to complexity by using Polar Code which is having O(NlogN) complexity [21] & invented by Erikan in 2008. Complexity of Polar code is not increase even though its block length increases. From the survey, I will implement Polar code on PLC Channel to reduce the complexity and improve BER using specific Block Length.

The rest of the paper is organized as follows. Section 2 describes PLC channel noise and its classification. QC-LDPC codes with Powerline Noise are presented in section 3, Polar Encoding and Decoding algorithm is summarized in section 4. Sections 5 describe simulation system arrangement Polar Codes. Conclusion is given in Section 6.

# 2. PLC CHANNEL NOISE AND ITS CLASSIFICATION

Noise in the PLC channel can be modelled as a cyclostationary process and its amplitude distribution at the same phase as the AC source can be modelled as Gaussian distribution. The variance is assumed to be the sum of three types of noise and it can be expressed as follows [10]: stationary noise, cyclical continuous noise and cyclical impulsive noise. The first category is a time invariant noise component. The second and third categories are the periodic noise components.

PLC Channel is modelled under Cyclo-stationary Gaussian environment which is more characteristic of a real PLC Channel. Reason for taking powerline channel as compared to other channel like AWGN and other wireless is there is no need to establish new infrastructure, data transmission speed is also high and cost will be reduce.

Channels such as a PLC channel are highly frequency selective in nature. Frequency selective channels provide different levels of attenuation at different frequencies making it tedious for efficient transmission and reception. Hence the available bandwidth can be divided into various sub channels and data transmission can be carried out on each of those sub channels simultaneously so that each of these sub channel have flat fading (constant attenuation across the bandwidth). This is called Frequency Division Multiplexing (FDM). A specific sub carrier is associated with each sub channel. The terms sub channel and sub carriers are often interchangeably used. The guard band is used separate sub channels by a certain frequency so that they do not overlap into each other and cause Inter Carrier Interference. The need of guard band is eliminated by allowing overlap of adjacent sub channels using Orthogonal Frequency Division Multiplexing resulting better bandwidth efficiency [17].

# 3. LDPC CODE WITH POWERLINE NOISE

QC-LDPC code is a type of LDPC. A (ht, k) QC code Cqc is a linear block code over GF(2) and depends upon the positive integers 't', 'h' and 'k' with the constraint k < ht. There have been many OC-LDPC codes that have been introduced previously. In order to design efficient QC-LDPC codes with better minimum distance, two methods based on finite geometries and circulant permutation matrices are evaluated [13], [14] and [15]. There are two conditions that are placed on a QC Code. First, every codeword should consist of 'h' sections of t' bits each. Second, every codeword, after a cyclic shift in QC code, should be a codeword in Cqc [12]. The circulant permutation matrices are used to generate the paritycheck matrices for the QC-LDPC codes. The column permutation operation is used to obtain matrices. The main positive reason of using the QC-LDPC codes over randomly generated regular LDPC codes is that the QC-LDPC encoding procedure is has a simpler structure [16]and easier to implement and the memory requirement is very less when compared to the LDPC codes. It helps to implement codes with large block lengths. Detail description is given below.

#### 3.1 LDPC Encoding

For QC-LDPC encoding, consider a parity check matrix  $\boldsymbol{H}$ , which are circulant permutation matrices. These circulant permutation matrices are generated by the permutations of a permutation matrix  $\boldsymbol{P}$  of size q \* q where parameter q should be a prime number. The parity check matrix  $\boldsymbol{H}$  is composed of permutation matrix and several of its circular shifts [16]. The matrix  $\boldsymbol{H}$  is filled row wise and once the first row elements are fixed, the other parameters of each block matrix  $\boldsymbol{P}$  follow the first row schedule. Hence, memory storage is reduced. The parity check matrices for both the regular and irregular QC-LDPC codes are constructed in similar ways.

#### 3.2 LDPC Decoding

There are two classes of decoding algorithms that were considered for decoding the QC-LDPC codes. First ,which is common iterative decoding algorithm for LDPC codes is SPA, which is a belief propagation algorithm [5] . It is a soft decision algorithm performs better than the hard decision algorithms. Several such schemes are proposed in [17], [18]. In the SPA, the variable nodes (v) collect the received signal and send its messages to its connected check nodes (c). The messages from all the connected v nodes are estimated and calculated at the c-nodes. These information results are sent back to the v-nodes. The information sent by a c-node to a v-node is based on the information that it receives from all the other v-nodes except the one it is sending the information

results to. One iteration is forms using this exchange of message and information results between the v-node and the c-node. Until the correct codeword is reached or until the maximum number of iteration limit is reached these iterations are carried out. After the end of iteration process, an entire codeword is estimated.

The other algorithm which is an iterative algorithm for a hard decision decoding is the Bit-Flipping algorithm. In this process, the decoding is done with the parity check matrix Hand received signal vector x. First, HxT is calculated and the non-zero elements are identified in it. After every bit node resolve the number of unsatisfied c-nodes, so largest number of unsatisfied c-nodes is found. The bits of x involving the unsatisfied c-nodes are 'flipped' from 0 to 1 or 1 to 0. This process is repeated until the maximum number of iterations is reached or until the term HxT = 0. Several of the bits are 'flipped' simultaneously during each of these iterations. To avoid the flipping of correct bits, in paper [17] proposed that only one bit should be flipped per iteration, largely increasing the number of iterations to get acceptable results. By considering all these constraints the SPA is selected for decoding.

#### 4. POLAR ENCODING AND DECODING

According to the noisy channel coding theorem it is possible to construct a code that can achieve Shannon's limit. Like many other capacity approaching codes, Polar codes are the first provably capacity achieving codes for any symmetric binary-input discrete memory less channels (B-DMC) which have low complexity encoding and decoding algorithms. And given the channel is symmetric; the achieved symmetric capacity is equal to the channel capacity. Complexities of encoding and decoding are both O(NlogN) where N is the block length [3]. Polar codes are based on *channel polarization* phenomenon.

#### 4.1. Channel Polarization

Based on "Channel Polarization" phenomenon Polar codes are the first "practical" codes that are known to achieve the capacity for a large class of channels which is invented by Arıkan, It suggests a simple scheme where we fix the inputs to the channels that are bad and transmit reliably over the clean channels without any coding. The rate of such a scheme approaches the capacity of the channel. The channel polarization phenomenon suggests using the noiseless channels for transmitting information while fixing the symbols transmitted through the noisy ones to a value known both to sender as well as receiver. For symmetric channels we can assume without loss of generality that the fixed positions are set to 0. The encoding as well as the decoding operation of polar codes can be implemented with O(NlogN) complexity, where N is the block length of the code[19]. Channel Polarization synthesizes N channel B-DMC then it split into noiseless channel approaching the capacity of I(W) or into a pure noise channel approaching 1- I(W)[19] . So we can use this sort of polarization to construct Polar codes by sending data through those channel with high capacity and fix the inputs through those channels with low capacity. Now when the information bits are encoded in the channel, in encoding structure of polar codes, there is the XOR operation is performed at channel combining stage of channel polarization

The two central topics of information theory are the compression and the transmission of data. Shannon, in his decisive work, dignified both these problems and resolute

their fundamental limits[15]. Since then the main goal of coding theory has been to find practical schemes that approach these limits.

#### 4.2. Code Construction

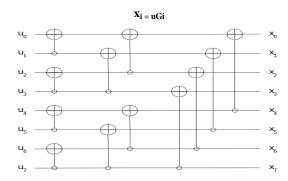

Originally, polar codes were constructed using a generator matrix created using the kronecker power of the base matrix  $F_2 = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$ . This construction method yields Polar codes whose lengths are powers of two. For example, the generator matrix of an **n=8** for Polar Codes Shown in figure.

Polar codes can also be illustrated using a graph representation. In this case, the information vector  $\mathbf{u}$  is presented on the left-hand side of the graph and the resulting decoded codewordx is obtained on the right-hand side. The  $\oplus$  symbols represent XOR operations[14].

$\overline{X}$  = [ $u_0 u_1 u_2 u_3 u_4 u_5 u_6 u_7$ ] $F_8$

$$F^{\otimes 1} = \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$$

$$F^{\bigotimes 2} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 \end{bmatrix}$$

$$F^{\otimes 3} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

We can verify that

Fig. 1: Graph representation of polar code [19]

It is also referred that Polar codes are based on the observation that specific bits in the input data going to be better protected from noise than others. As described in [19]that as the code length N grow larger, individual bits in the input word tend to become either very good or very badly protected. By identifying those good protected bit indices in the information vector and using those to transmit information Polar codes are constructed. The set of good protected bits are called *information set* while the remaining bits are from the *frozen set*, value of which is known by both the encoder and the decoder.

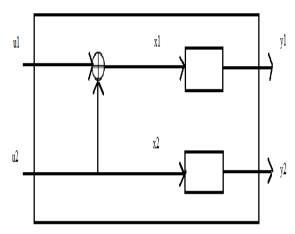

Now when bit are encoded in the channel they are XORed with each other .At channel combining stage of channel polarization which is shown in fig.3 which shows the first recursion manner of n=1 for channel  $W_n$ where  $N=2^n,N>=0$ .

Fig. 2: Combining of channels W2 [19]

### 4.3 Decoding Algorithm

#### **Successive Cancellation**

The above procedure can be seen as transmitting a codeword and decoding at the receiver with a successive cancellation (SC) decoding strategy. Decoding of polar code can be done using Successive Cancellation decoding scheme. Frozen set are kept fix, Information set is passed during decoding.

For each i=1,2,...,N. If  $u_i$  is frozen, set  $\hat{u}_i=0$ , otherwise generate decision,

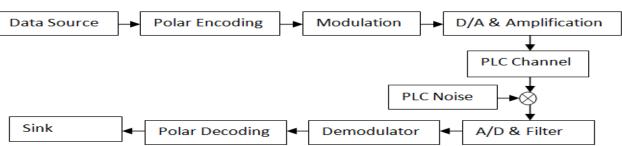

Fig.3: Proposed Simulation System arrangement

$$\hat{u}_i = \left\{ \begin{array}{ll} 0, & \quad if \ L_N^{(i)}(y_1^N, \hat{u}_1^{i-1}) \geq 0 \\ 1, & \quad otherwise \end{array} \right.$$

Where

$$L_N^{(i)}\left(y_1^N, \hat{u}_1^{i-1}\right) = log \frac{W_N^{(i)}(y_1^N, \hat{u}_1^{i-1}|0)}{W_N^{(i)}(y_1^N, \hat{u}_1^{i-1}|1)}$$

By using above formula, channel which tends rate of one is to polarize in one noise free and the other channel which tends to zero is noisy channel.

The successive cancellation decoder has complexity O(NlogN). Since the decoder ignores the future frozen bits, it is suboptimal yet, it achieves the symmetric capacity.

#### 5. SIMULATION SYSTEM

The simulations were executed on a 3.1 GHz PC running Matlab R2010B below shows the simulation system design blocks. Our proposed system is shown in Fig. 3 that will implement on PLC.Fig.4 Shows PLC Channel Matlab simulation circuit [22].

#### 6. CONCLUSION

From the Survey, I Conclude that LDPC Code works better when the block length is small but as block length increase complexity increase. To overcome this QC-LDPC code with low memory requirement and easy implementation structure is used. In QC-LDPC BER improve when code rate decrease, block length increase.

Polar Code which is first provably capacity achieving codes for any symmetric binary-input discrete memory less channels (B-DMC) which have low complexity encoding and decoding algorithms O(NlogN). It also work well for large block length and work well when code rate increase. From this survey I will implement Polar Codes on PLC Environment.

Future Work is, this work can be extended upto wifi.

#### 7. REFERENCES

- [1] "Power line communications: state of the art and future trends," N. Pavlidou, A. J. Han Vinck, J. Yazdani, and B. Honary *IEEE Communications Magazine*, pp. 34–40, April 2003

- [2] "Physical and regulatory constraints for communication over the power supply grid," M. Gebhardt, F. Weinmann, and K. Dostert *IEEE Communications Magazine*, vol. 41, no.5, pp. 84–90, May 2003.

- [3] H. Hrasnica, A. Haidine, R. Lehnert, *Broadband Powerline Communications: Network Design*, John Wiley & Sons, 2005.

- [4] Powerline Communications Network Technology eLibrary [Online]. Available: http://plugtek.com/, accessed Mar. 2012.

- [5] "Low density parity check codes," R. G. Gallager, IRE Transactions on Information Theory, vol. IT-8, pp. 21– 28, Jan. 1962.

- [6] "A recursive approach to low complexity codes," M. Tanner, IRE Transactions on Information Theory Theory, vol. IT-27, 1981.

- [7] "Good error-correcting codes based on very sparse matrices" D. J. C. MacKay, *IRE Transactions on Information Theory*, 1999.

- [8] "Performance Evaluation of LDPC Codes on PLC Channel Compared to Other Coding Schemes" N. Andreadou, C. Assimakopoulos, F.N. Pavlidou, IEEE International Symposium on Power Line Communications (ISPLC), pp. 296–301, 26–28 March 2007.

- [9] "Near Shannon limit error-correcting coding and decoding: Turbo codes" C. Berrou, A. Glavieux, and P. Thitimajshima, *Proceedings of the IEEE International Conference on Communications*, Geneva, Switzerland, May 1993

- [10] "A study on performance of LDPC codes on power line communications", T. Wada, *IEEE International Conference on Communications*, vol. 1, pp. 109–113, June 2004

- [11] "A Comparative Performance Study of LDPC and Turbo Codes for Realistic PLC Channels" Gautham Prasad, Haniph A. Latchman, Youngjoon Lee, Weiler A. Finamore, 2014 18th IEEE International Symposium on Power Line Communications and Its Applications.

- [12] W. Ryan, S. Lin, Channel Codes: Classical and Modern, Cambridge University Press, 2009.

- [13] "Low Density Parity Check Codes on Finite Geometries: a Rediscovery and New Results", Y. Kou, S. Lin, M. Fossorier, *IEEE Trans. Inform. Theory*, Vol. 47, pp. 2711-2736, 2001.

- [14] R. M. Tanner, D. Sridhara, A. Sridharan, T. E. Fuja, D. J. Costello "LDPC block and convolutional codes based on circulant matrices", *IEEE Trans. Inform. Theory*, Vol 50, No. 12, pp. 2966-2984, 2004.

- [15] M. Fossorier, "Quasi-Cyclic Low Density Parity Check Codes from Circulant Matrices, *IEEE Trans. Inform. Theory*, Vol. 50, pp. 1788-1794, 2004.

- [16] "Conquering the Harsh PLC Channel with QC-LDPC Codes to Enable QoS Guaranteed Multimedia Home Networks", Y. Lee, A doctoral dissertation submitted to the University of Florida, 2013.

- [17] "QC-LDPC codes and their performance on Powerline Communications Channel", N. Andreadou, F. Pavlidou, Proc. IEEE ISPLC, pp. 244-249, Apr 2009.

- [18] "Quasi-Cyclic LDPC codes for fast encoding" S. Myung, K. Yang, J. Kim, *IEEE Trans. Inform. Theory*, Vol. 51, pp. 2894-2901, Aug 2005.

- [19] "Efficient Design and Decoding Of Polar Codes" Peter Trifonov, Member, IEEE Transactions On Communications, Vol. 60, No. 11, November 2012.

- [20] "Information Theory and Coding" By-Anoop Singh Poonia

- [21] "Channel Polarization: A Method For Constructing Capacity-achieving Codes" Erdal Arıkan ISIT 2008, Toronto, Canada, July 6 - 11, 978-1-4244-2571-6/08©2008 IEEE